The IIS Chip Gallery

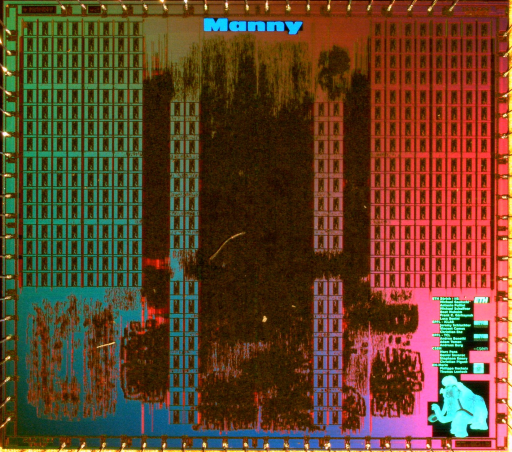

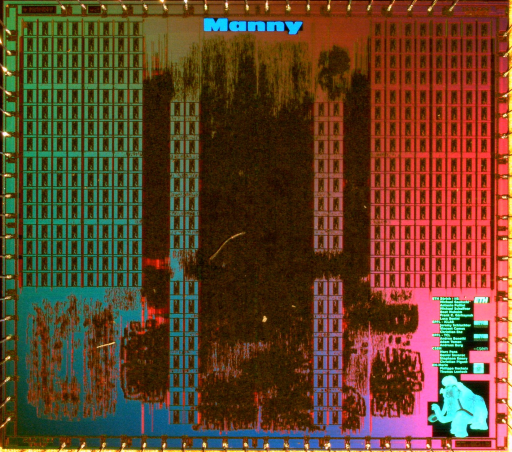

Manny (2015)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 180 |

| Manufacturer | ALP |

| Type | Research |

| Package | DIP64 |

| Dimensions | 7201μm x 8160μm |

| Gates | 2 MGE |

| Voltage | 0.6 V |

| Power | 3 W @0.6V 1.5MHz |

| Clock | 1.25 MHz |

Manny is one of three chips manufactured using the 180nm technology of EM Microelectronic, making it a completely Swiss project. These chips were designed as part of the Nano-Tera project IcySoC.

These chips are designed to take advantage of:

The base of the system is a PULP system with four cores, 64 kByte of L2 memory, 16 kBytes of TCDM and 4 kBytes of shared instruction cache. This system is then augmented by a shred approximate single precision floating point unit that has a worst case error of 8 ULPs. In addition there is a generic hardware accelerator interface that allows in-exact accelerators to be connected to the main system. In this chip there are two generic FIR filters that have their computational rounds optimized using pruning and speculation.

This version uses a special subthreshold standard cell library and memory macros designed to operate at 0.6V.

These chips are named after Ice Age characters. We needed three names, and the movie name resembled the project name (Ice Age,IcySoC). After all the chips are meant to be low power, and therefore should be cold as ice. The main difference between the chips is that a different standard cell librray was used for the design (Manny has only two generic FIR filters the other two designs have four due to area limitations). These are fairly large chips, each has a core area of more than 50 sqmm. The three chips are: