The IIS Chip Gallery

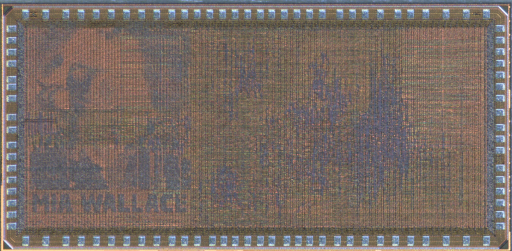

Mia_Wallace (2015)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Research |

| Package | QFN64 |

| Dimensions | 3950μm x 1875μm |

| Gates | 2 MGE |

| Voltage | 1.2 V |

| Power | 1 mW @1.2V 1MHz |

| Clock | 400 MHz |

Mia Wallace is the first chip of the new generation of chips from the PULP project. It has been designed to have sufficient memory (256kBytes) and interfaces to be used in a wide variety of practical applications.

Mia constains four modified Or10n cores that have support for vector instructions as well as a functional debug interface. The chip has two power domains, the low-power optimized cluster domain is expected to work down to 0.3V. At this operating point, the standard SRAM macros will not be functional, this is why, part of the TCDM bank as well as the instruction cache has been implemented using standard cell based memories. The substrate voltage of the cluster can also be controlled externally allowing different body biasing strategies to be implemented.

The chip also includes two FLL (Frequency locked loops) that are able to generate the desired operating frequency (0-500MHz) from a simple 32kHz crystal oscillator independently for both the cluster and the surrounding SoC domain that contains the large L2 memory and the interfaces which consist of multiple SPI interfaces, a standard UART as well as a JTAG port.

Mia includes a convolutional accelerator (HW Convolution Engine (HWCE) capable of computing 2x 16-bit pixels per cycle.

As we have no access to non-voltaile memory for this particular technology, there is a small ROM that contains the necvessary routines to initialize the chip, communicate with an external flash memory and load the memory. Then the control is passed to the program that has been just loaded.

As can be imagined we are all fans of Pulp Fiction and this series of PULP chips will be named after characters from this movie. Mia Wallace (or shortly Mia) is this chip. Giving such names makes it easier for us to communicate within the group, it is much easier to say 'Mia' instead of the '4-core, 256 kByte L2, pulp chip taped out in April 2015 using umc 65'.

Watch a video of Mia Wallace in action for the first time in this video. Until this time we had tested the chips mainly on our ASIC tester. This is the first time that Mia Wallace ran on our new development board.