The IIS Chip Gallery

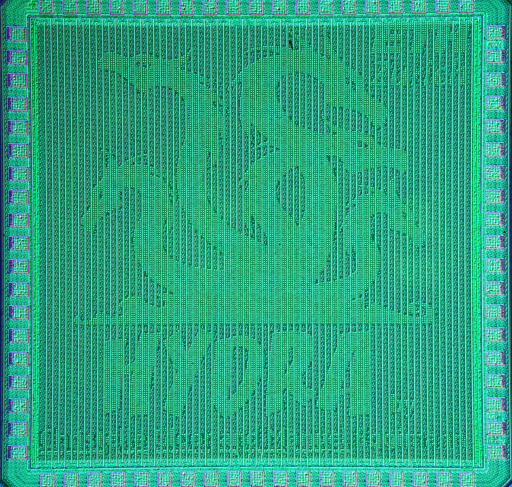

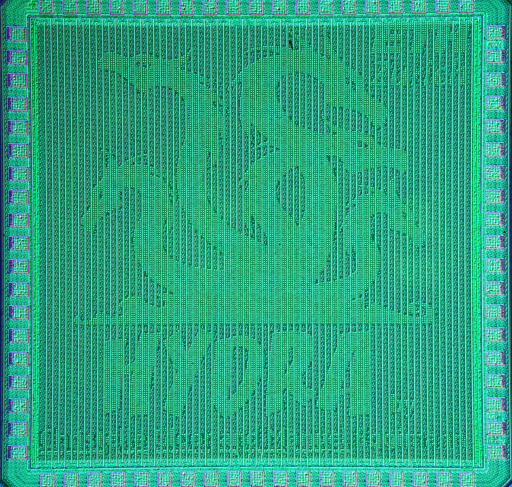

Hydra (2016)

Additional pictures below, click to see larger versions

by

| Application | Machine-learning |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN64 |

| Dimensions | 1875μm x 1875μm |

| Gates | 1400 kGE |

| Voltage | 1.2 V |

| Power | 783.4 mW @ 1.20 V, 333 MHz |

| Clock | 333 MHz |

Edge aware filters are an important precursor to various graphics processing algorithms. An algorithm which allows for an efficient hardware implementation of a Permeability Filter has been developed in collaboration with Disney Research Zurich recently. In this semester project we nished implementing one part of the algorithm as proposed in the previous paper and developed a hardware architecture which realizes it. The hardware was implemented on an ASIC prototype built in umcL65 technology. It filters 30 frames per second in HD-resolution ( 1280× 720 pixels) for a single colour channel. It operates with a floating point precision of 24 bits. An efficient design has been found in order to handle the large amounts of data which need to be processed. Some challenges relating to the data access patterns of the SRAMs had to be solved. The design is easily scalable for higher resolutions or multiple channels.

The chip is called Hydra, because the students involved in the design are all members of the secret group from a well-known movie franchise. This chip will be part of their top-secret plan to take over the world. All the assembled superheroes will nto be able to stand against this superplan. stay tuned.

Drawing on the chip taken and adapted for IC production from pathfinderlinden as cc-by.