The IIS Chip Gallery

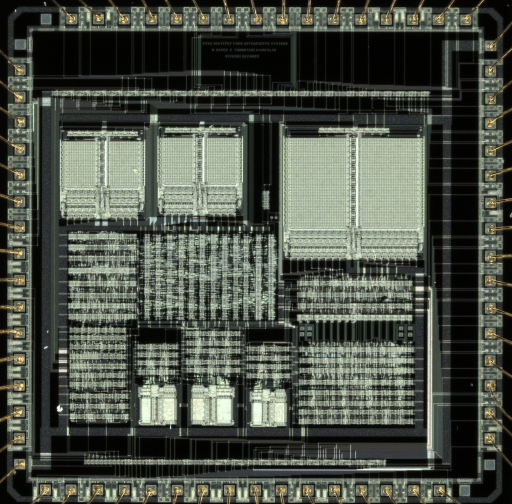

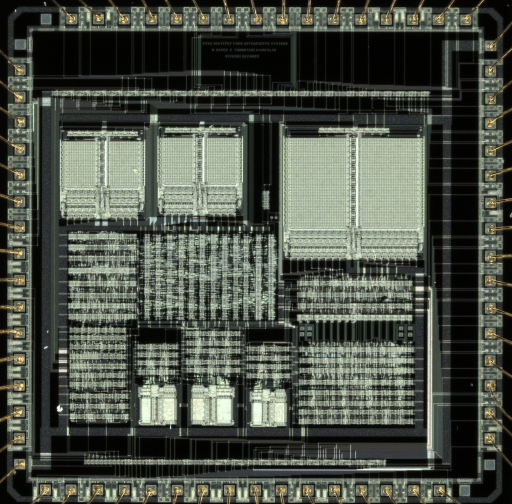

Viterbi (1987)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 2000 |

| Manufacturer | Faselec |

| Type | Research |

| Package | DIP64 |

| Dimensions | 6400μm x 6400μm |

| Gates | 9 kGE |

| Voltage | 5 V |

| Power | 100 mW |

| Clock | 20 MHz |

Among the error-correcting codes used in digital communications convolutional codes are often preferred for their superior coding gains. Typical applications are found in depp space communication, mobile radio, and data transmission over the electrical supply network. The best-known decoding scheme follows the Viterbi algorithm, a special case of dynamic programming applied to a trellis graph. The high computational burden at the reciever end restricts the use of microprocessor to applications with data rates of a few kbit/s, however.

In contrast, an ASIC developed at the IIS runs at up to 300kbit/s and dissipates only 100mW when applied to 64 kbit/s PCM telephone signals. Based on a rate 1/2 code witrh constraint length 7 and making use of soft decision decoding a coding gain of more than 5.2dB is obtained.

The circuit has been designed from a standard and macro cell library for a 2um double metal poly gate n-well CMOS process and contains 35'000 transistors on a die of 35mm^2. Testability is ensured by scan-path and block isolation techniques.

A digital transmission channel based on a AWGN model built around the decoder vividly demonstrates the superiority of coded over uncoded transmission by way of audio signals.