The IIS Chip Gallery

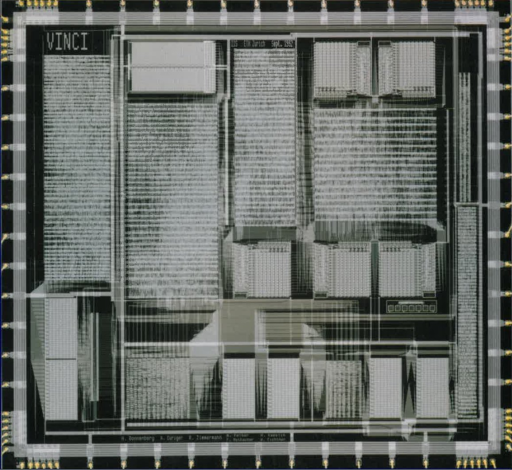

Vinci (1992)

by

| Application | Cryptography |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Research |

| Package | PGA132 |

| Dimensions | 10000μm x 10780μm |

| Gates | 60 kGE |

| Voltage | 5 V |

| Power | 1250 mW(25 MHz, 5V) |

| Clock | 25 MHz |

This work included the chip implementation of the International Data Encryption Algroithm (IDEA). This algorithm encrypts and decrypts 64-bit blocks of data using a 128-bit user specified key. The cipher relies on combining operations from three different algebraic groups and is proposed to become a European encryption standard.

The resulting VLSI circuit operates at 177 Mbit/sec data encryption rate (@25 MHz clock frequency). Standard encrypt and decrypt modes ECB, CBC, CFB, OFB and MAC are available. In addition, fast encrypt and decrypt modes CBC8, CFB8, and OFB8 have been implemented to fully exploit inherent pipelining and parallelism. Finally, the device complies fully to security standards.

The VLSI circuit is the first implementation of IDEA. It achieves data rates more than 8 times faster tgan the fastest silicon implementation of the de facto block encryption standard DES. This has been achieved by: