The IIS Chip Gallery

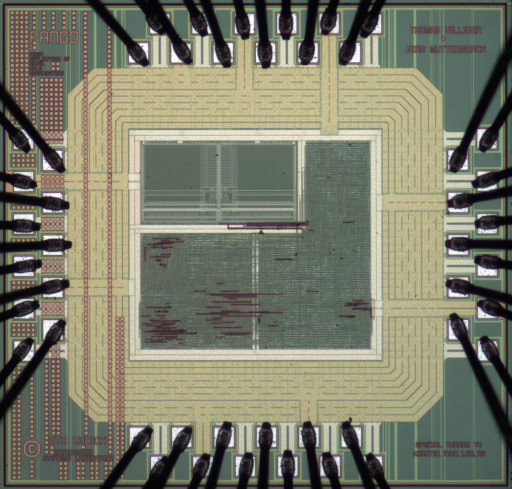

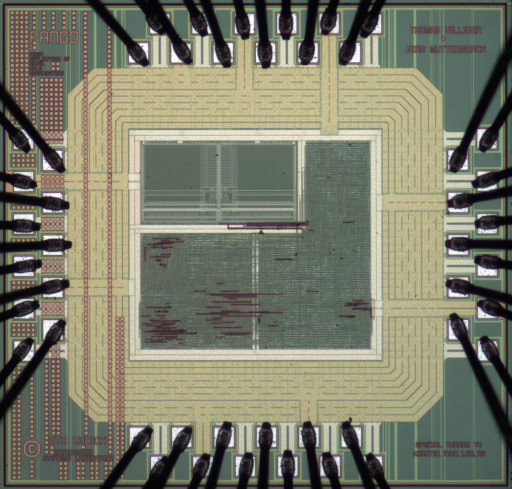

Fango (1999)

by

| Application | Cryptography |

| Technology | 250 |

| Manufacturer | STM |

| Type | Research |

| Dimensions | 1500μm x 1500μm |

| Voltage | 2.5 V |

| Clock | 400 MHz |

The technical progress in CMOS technologies, increase in available die size, and the demand for short time-to-market ask for integration of large systems on a single chip. Higher clock frequency and larger area make proper clock distribution difficult. Complex systems often require a multitude of clocks on a common die, therefore asking for reliable synchronizers between independent clock domains.

A Globally Asynchronous Locally Synchronous (GALS) design methodology facilitates clocking of large systems on silicon as it partitions a system into several independently clocked modules which communicate in self-timed fashion. Every synchronous module is surrounded by a so-called asynchronous wrapper that manages all the data transfers. The actual functionality remains unchanged inside the locally synchronous blocks, such that well established design flows can be used. The local clocks are generated within the wrappers and are stopped when there is no data to process in the synchronous block. The partitioning into modules results in enhanced modularity and reusability, and the decoupled timing constraints between modules leave more options for optimization.

FANGO, a cipher chip performing the SAFER-K64 algorithm has been implemented to validate the feasibility of GALS.