The IIS Chip Gallery

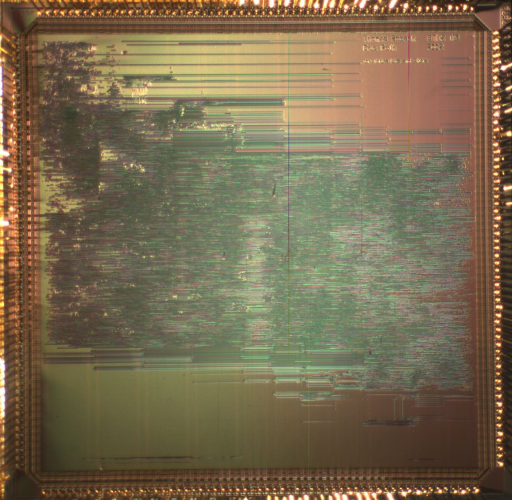

Multimedia_SoC (2003)

by

| Application | Industrial |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | PGA208 |

| Dimensions | 5000μm x 5000μm |

| Voltage | 2.5 V |

| Clock | 100 MHz |

A flexible stream processor architecture optimized for networked multimedia devices has been developed and integrated on a System-on-Chip (SoC). The chip contains two Stream Processors (SP), a SparcV8 compliant host CPU, a DMA engine, and various interface controllers interconnected by an AHB system bus.

The stream processors perform low-level processing tasks on the multimedia data streams, whereas the host CPU controls the system. Every stream processor consists of a general-purpose 32-bit RISC processor with a Stream Processing Extension (SPE). The RISC processor defines application-specific operations and micro programs in the SPE. These operations can be triggered with special instructions during the processor's program execution. The SPE is optimized to efficiently access data streams and to execute multiple operations in parallel. It is built of memories and various functional blocks performing different arithmetic operations. Furthermore, custom operations can be implemented in a fine-grained mesh of reconfigurable logic cells (RC). All components are interconnected by a non-blocking, programmable network.

The system has been integrated on a 5x5mm2 chip die using a 0.25um CMOS technology. It runs at a system clock frequency of 100MHz.