The IIS Chip Gallery

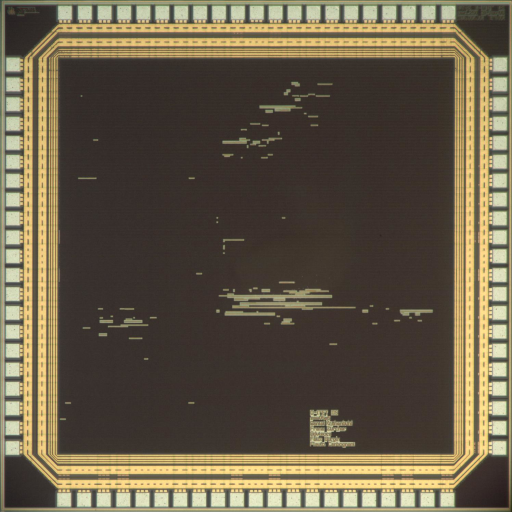

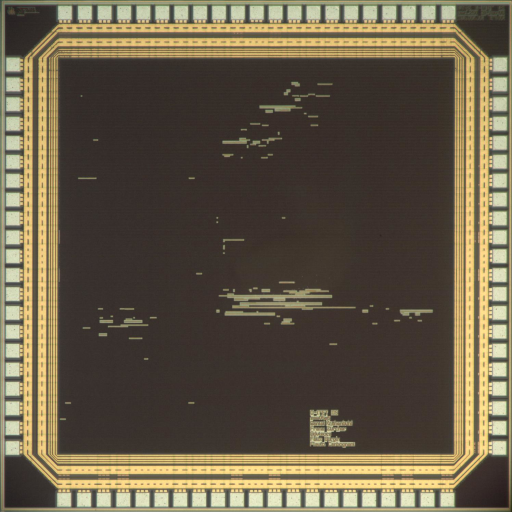

DirMic (2006)

by

| Application | Audio |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Clock | 0.022 MHz |

In this project a new constant-coefficient FIR filter architecture has been developed, specifically designed for a VLSI adaptive directional microphone in hearing aids. Gatelevel simulations targeting a 0.25um standard CMOS process point out relevant power savings compared to both the fully time-shared reference design (-80%) and a recently published low-power circuit (-32%), with a limited 11% area overhead compared to the latter one.

The proposed architecture named 'Hierarchical Computation Sharing Canonical-Signed-Digit' is based on the transposed form of the filter, which means that all multipliers share the same variable (filter) input x. Starting from the computing sharing multiplier, where common factors among different partial products are precomputed and then combined, the presented architecture decreases the number of additions further by:

Note that all coefficients are assumed to be positive and products of negative ones (c1, c3, c5, c7) are inverted right before output. A total number of 10 adders is required for multiplying the 9 coefficients with the input value x.