The IIS Chip Gallery

ASPE_A (2008)

Additional pictures below, click to see larger versions

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Reserach Project |

| Package | PGA120 |

| Dimensions | 4000μm x 2500μm |

| Gates | 400 kGE |

| Voltage | 1.8 V |

| Clock | 250 MHz |

In the near future, WLANs will spread more and more into the homes, where the increasing data traffic (e.g. music, video streaming) calls for higher throughput than the currently supported 54 Mbps which do not suffice for real-time streaming of high-quality audio/video for multiple users. To this end, standards that embed multiple-input multiple-output (MIMO) techniques to enable higher throughput, are reaching the market (e.g. IEEE 802.11n standard).

In this project, the hard computational kernels of a 2x2 MIMO-OFDM receiver were implemented on a platform with two reconfigurable instruction set processors (RISP). The partitioning and mapping of the receiver onto two RISPs respects the structure of the employed algorithms. The first RISP performs the OFDM frame synchronization and OFDM processing, for which the hard computational kernels are mainly correlations and fast Fourier transforms. The second RISP executes the MIMO detection, where matrix inversion and matrix-vector multiplications are the hard computational kernels (see column to the right). For the 2x2 MIMO-OFDM receivever to operate in real time, both RISPs have to run at a clock frequency of 250 MHz.

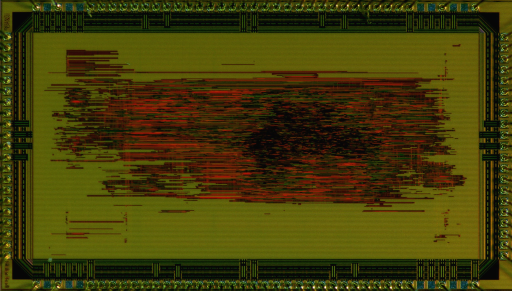

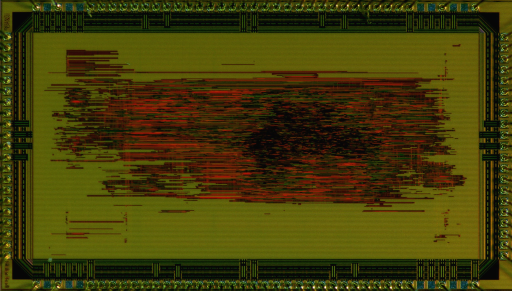

The figure below shows the floorplan of the OFDM processing RISP. The design runs at a clock frequency of 250 MHz (after backend design) and occupies an area of 3.95 mm2 on a 180 nm CMOS process.