The IIS Chip Gallery

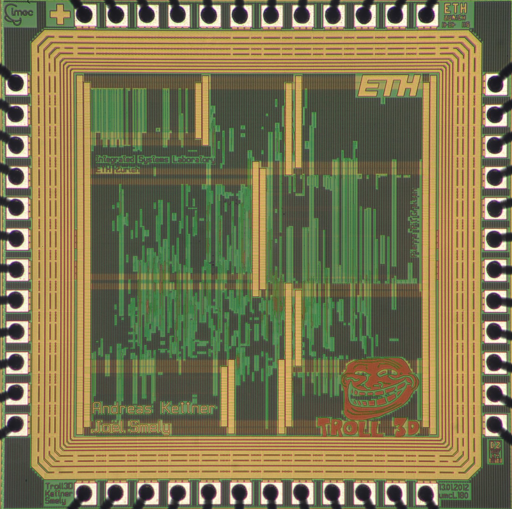

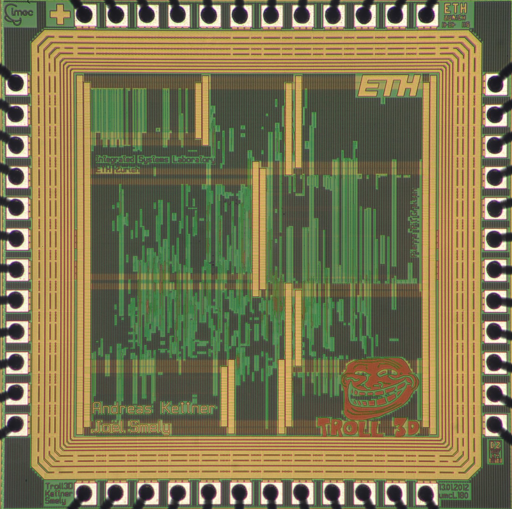

Troll3D (2011)

Additional pictures below, click to see larger versions

by

| Application | Graphics |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 80 kGE |

| Voltage | 1.8 V |

| Power | 100 mW, 200MHz |

| Clock | 200 MHz |

Depth estimation or disparity estimation from stereoscopic video streams has been extensively treated in the research community and also in industry. Several efficient algorithms that are capable of calculating real-time depth information have been presented in recent years. However, the gap between fast execution and low estimation quality and slow execution and good estimation quality is still considered an open research challenge. Good quality is currently obtained for algorithms that employ costly global optimization techniques, whereas real-time variants employ poorer-performing local or semi-global methods.

Recently, a new approach to local depth estimation has tried to close the gap. The key idea behind these new types of algorithms is to apply local filtering instead of global optimization by imposing data constraints on the matching costs. Thus, in a first step we calculate matching costs as in traditional local-window methods and in a second step we filter the 3D costs with a data dependent filter (a guided filter in our case). Finally, standard winnertake- all selection is performed to find the minimal cost and hence the disparity.

In this chip, the disparity estimation algorithm with cost filtering has been implemented in 180 nm CMOS. The main challenge has been the high memory requirements of the cost filter