The IIS Chip Gallery

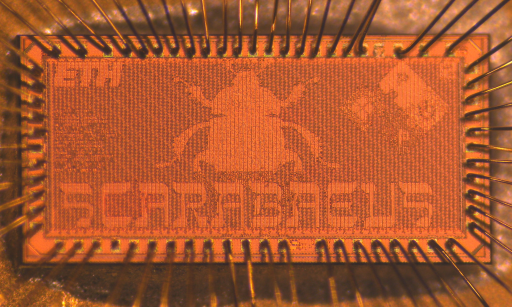

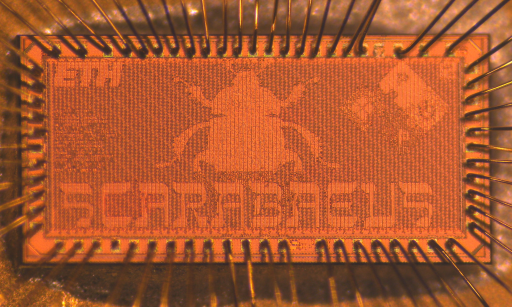

Scarabaeus (2018)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 2626μm x 1252μm |

| Gates | 1200 kGE |

| Voltage | 1.2 V |

| Power | 45.97 mW @ 1.2 V, 200 MHz |

| Clock | 200 MHz |

Scarabaeus implements an Ariane-based RISC-V (RV64IMC) SoC including 64 kByte L2 memory, 4 Kbyte Data and Instruction cache. In this project the existing PULP modules are extended by a Platform Level Interrupt Controller (PLIC) as specified by the RISC-V standard, and by a DMA controller that is capable of transferring arbitrarily shaped, aligned and strided data parallelepipeds of up to four dimensions on a 64 bit AXI bus.

The chip also includes a HyperBus controller for the Cypress HyperRAM that has been re-written from scratch. This interface contains 13 I/O Pads occupies the lower side of the chip. The control logic has been placed in between the pads and occupies less than 10 kGE including clock synchronization between two independent clock domains (HyperBUS 166MHz and system AXI 250MHz). When operating with long bursts the effective bandwidth is 327 MB/s.

The chip also includes several peripeharls, a JTAG port that can be used for programming, 8 GPIOs and an UART. Finally the chip also contains an 8-bit RISC processor called Fireore (Fiercely Immature, Risky, Empirically Obscure, Radical Easteregg). Fireore uses the AOX-01 instruction set architecture (AetherOre eXecutable Version 01), which specifies a four-class reduced instruction set with three 8-bit special-purpose registers.

The chip has been affectionally named after a Dung Beetle. Scarabaeus is a Specifically Crafted Acronym Referencing an Ariane in a Brilliantly and Artistically Engineered Unprecedented SoC.