The IIS Chip Gallery

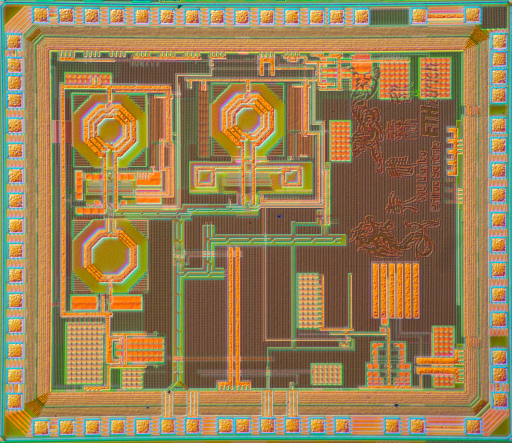

TimesADPLL (2018)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | SMIC |

| Type | Research |

| Package | QFN56 |

| Dimensions | 2000μm x 1711μm |

| Voltage | 1.2 V |

| Power | < 5 mW (@40MHz, 1.2V) |

| Clock | in:40 MHz out:3 GHz |

The TimesADPLL features an power efficient wide loop bandwidth fractional-N all digital PLL (ADPLL) implementation, which resolves the fractional phase error with the help of high performance data convertors in voltage domain, achieving sub-1ps RMS jitter integrated from 100kHz to 40 MHz offset frequency.

The logo on the chip is in ancient seal style Chinese font. This word comes from the famous book originates concept of Yin-yang "the book of Changes" which was written 3000+ years ago (Refer to this page for more information). The word is from the "Nine in the third place" which literally means:

All day long the superior man is creatively active. At nightfall his mind is still beset with cares. Danger. No blame.

This alludes to the fact to how this chip was finalized in a rush in just one month.