The IIS Chip Gallery

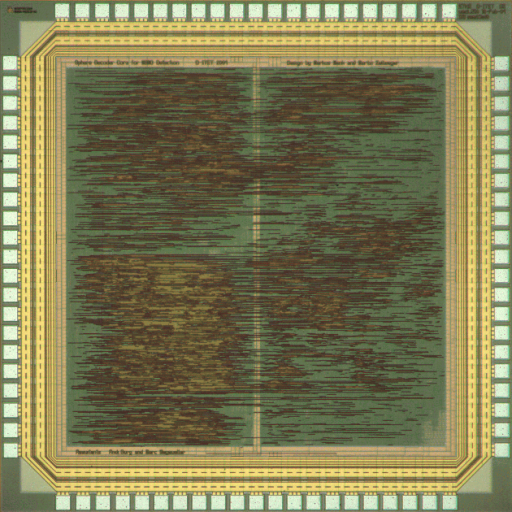

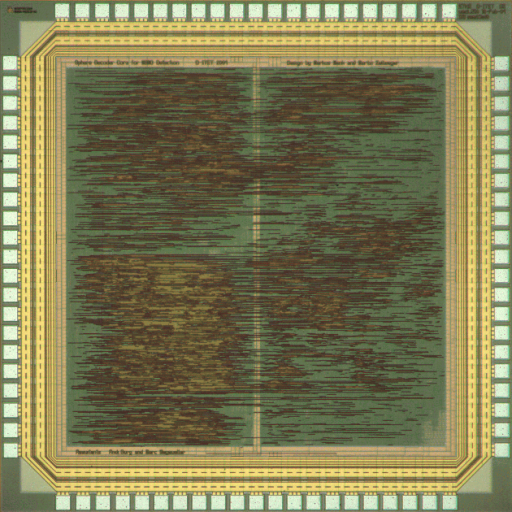

Sphere (2004)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 120 kGE |

| Voltage | 2.5 V |

| Power | 357.3 mW, 50MHz, 2.5V |

| Clock | 53 MHz |

Maximum likelihood (ML) detection can be used to achieve optimum bit error rate (BER) performance in multiple-input multiple-output (MIMO) communication systems and in a variety of other problems in wireless communications. Unfortunately, the complexity of a straightforward implementation with an exhaustive search grows exponentially with rate and quickly becomes prohibitive.

Sphere decoding (SD) is an algorithm that significantly reduces the average complexity of the ML detection problem. So far, only DSP implementations of the algorithm have been reported which can not achieve sufficient throughput to meet the requirements of wideband MIMO communication systems.

In this project, the worlds first VLSI implementation of the algorithm has been realized. The ASIC performs MIMO detection in a 4x4 system with 16-QAM modulation and achieves a throughput of 80 Mbps at 20 dB SNR, outperforming other MIMO detection ASICs in terms of throughput and BER performance. The key contributions of this work are an innovative high-level architecture that is optimized for the tree-pruning procedure that is used in the SD algorithm, and adaptations of the original algorithm to reduce the critical path of the circuit.

The project was awarded the Prix du Jeune Entrepreneur of the Section Suisse des Conseillers du Commerce Extérieur de la France.