The IIS Chip Gallery

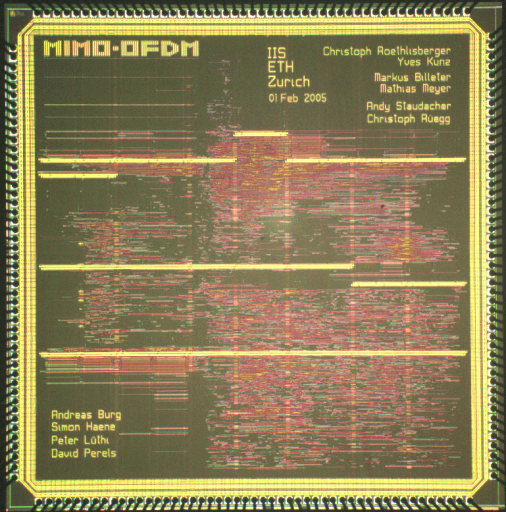

MIMO_OFDM (2005)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | PGA144 |

| Dimensions | 5000μm x 5000μm |

| Voltage | 2.5 V |

| Clock | 80 MHz |

Multiple-Input Multiple-Output (MIMO) systems employ multiple antennas at both transmitter and receiver in order to significantly improve link reliability and throughput of wireless communication systems. These gains come at no additional transmit power or bandwidth expenditure. MIMO is considered the key enabling technology for future wireless local area networks (WLANs) and wireless local loop systems targeting, peak data rates of up to 1 Gbps.

While ASICs for the IEEE 802.11a standard have been presented, little is known about suitable VLSI architectures for MIMO-OFDM systems and the silicon complexity for their implementation.

Goal of this project was to realize an ASIC implementation of a MIMO-OFDM WLAN transceiver with up to four transmit and receive antennas. The design supports datarates of up to 192 Mbps and constitutes one of the fastest WLAN ASIC realizations to date. Its architecture has been prototyped on the MIMO-OFDM testbed and comprises the complete baseband processing part including de/modulation, frequency offset estimation and compensation, frame start detection, and the MIMO detector.

The ASIC with a die area of 25 mm2 was manufactured in a 0.25um 1P/5M CMOS technology. It is running at a system clock frequency of 80 MHz.

This chip is a combined effort of three separate semester theses. The work was coordinated to result ina final large ASIC.