The IIS Chip Gallery

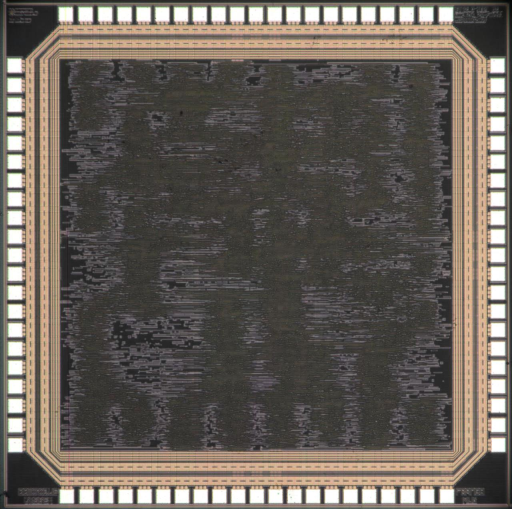

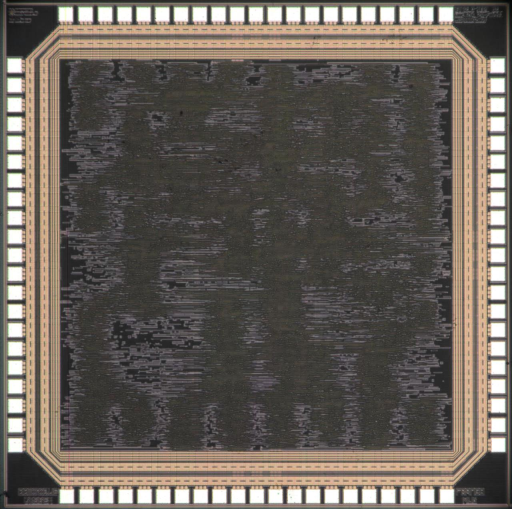

Fastcore (2003)

by

| Application | Cryptography |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 120 kGE |

| Voltage | 2.5 V |

| Clock | 166 MHz |

In 1997 the Rijndael algorithm has been selected as the new advanced encryption standard (AES). Since then numerous software and hardware implementations have been presented.

This AES implementation combines an encryption and a decryption engine which can operate concurrently. In this combination, the optimization of the inherently more complex decryption engine to match the timing of the encryption part is an important challenge. Besides the straightforward ECB mode, the OFB, CFB, and CBC modes of the standard are also supported.

The design was implemented in a 0.25um 5-metal CMOS process using a core area of 3.56mm2. The measured maximum clock frequency is 166MHz. This leads to a throughput between 1.52Gb/s for a key length of 256bits and 2.12Gb/s for a 128bit key. Operating encryption and decryption in parallel effectively doubles these numbers, but is currently constraint by the IO limitations of the chip. Herewith, the design is one of the fastest available AES implementations.

The result of this work has been used in another project for the development and experimental verification of a differential power attack (DPA) method.