The IIS Chip Gallery

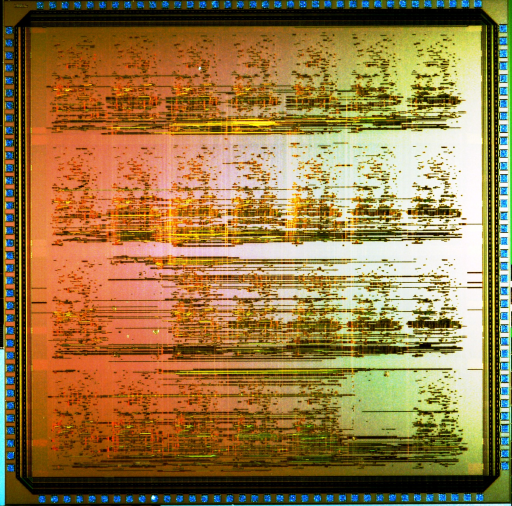

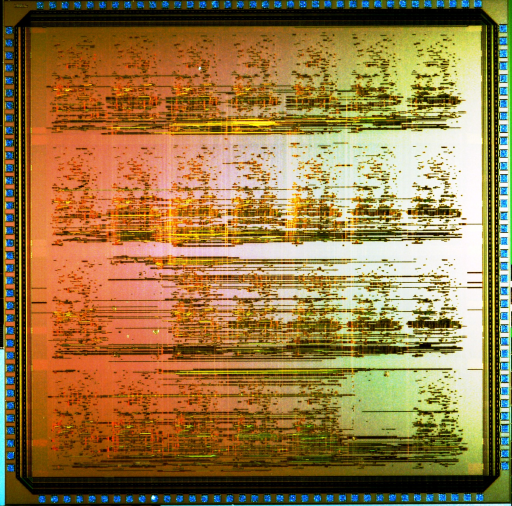

Shirkhan (2003)

Additional pictures below, click to see larger versions

by

| Application | Test |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | PGA144 |

| Dimensions | 5000μm x 5000μm |

| Gates | 800 kGE |

| Voltage | 2.5 V |

| Clock | 200 MHz |

This test chip contains 25 GALS modules that communicate using 5 different bus architectures. Each module consists of a custom designed 4-bit microcontroller that is able to emulate traffic patterns of a larger SoC design. This chip is used to evaluate proposed bus architectures for GALS.

This chip was a very good example of how in academic environments additional constraints end up being a problem. This particular chip was manufactured using UMC 0.25um technology, which had a minimum size of 5x5mm. However, if your design was larger you would pay automatically the price of another 5x5mm module. We realized quite late in the design process that we would need 1-2 mm2 more area if we wanted to achieve our designed speed of 300MHz. However, this would bring us over the limit for this block and double the cost of the chip. We ended up sacrificing a bit on the max speed (which reduced the area) and squeezed in the design. As a result our design ended up working 30% slower than we could have managed. Some of the reviewers for our papers also pressed this point. Technically, if the pricing was done differently, we would have just paid 5% extra area and gotten 30% more speed, but in this case, we would have paid the price of 100% more area.