The IIS Chip Gallery

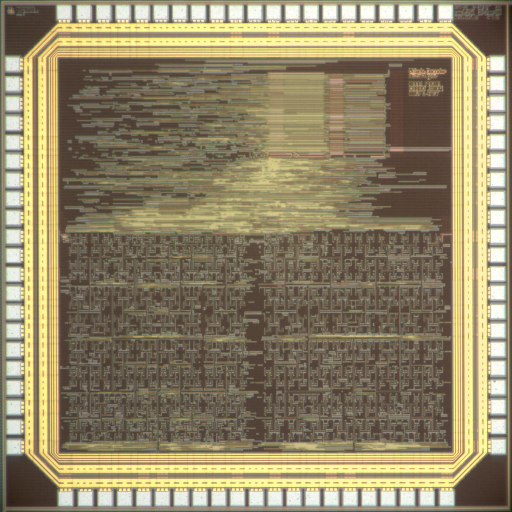

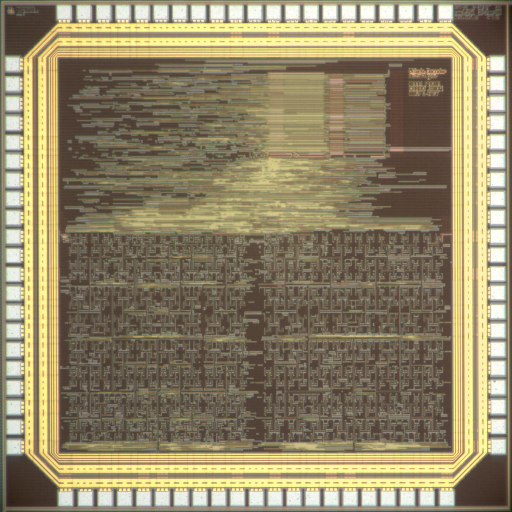

Viterbi (2006)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 30 kGE |

| Voltage | 2.5 V |

| Power | 50 mW, 1.75 V |

| Clock | 54 MHz |

Channel decoding is certainly one of the most powerhungry operations in wireless receivers. In particular, this work focuses on maximum-likelihood sequence detection of noisy convolutionally encoded data by the Viterbi decoder for IEEE 802.11a WLAN.

In order to minimize the dissipation in the clock distribution network, it was decided to apply resonant clocking. Sequential cells are triggered by very slowly varying sinusoidal waves. This gives rise to the following issues:

The first two points translate into relevant clock skew. They have been addressed by implementing a level-sensitive two-phase clocking strategy. Additionally, the trees associated with the two phases are routed as H-trees. Low-capacitance low-resistance clock trees have been obtained by routing the H-trees on the two highest metal layers. Finally, the waste of energy due to cross-over currents has been minimized by re-designing the latches.

The integrated decoder, with about 30,000 gate equivalents and 77 MHz maximum frequency, is one of the largest and fastest application-oriented designs with resonant clocking ever implemented and tested on silicon.