The IIS Chip Gallery

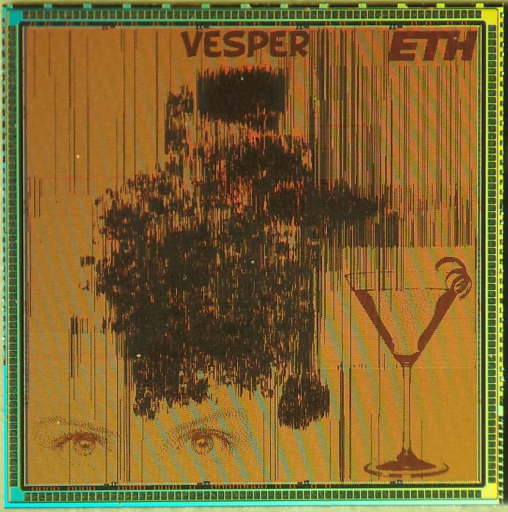

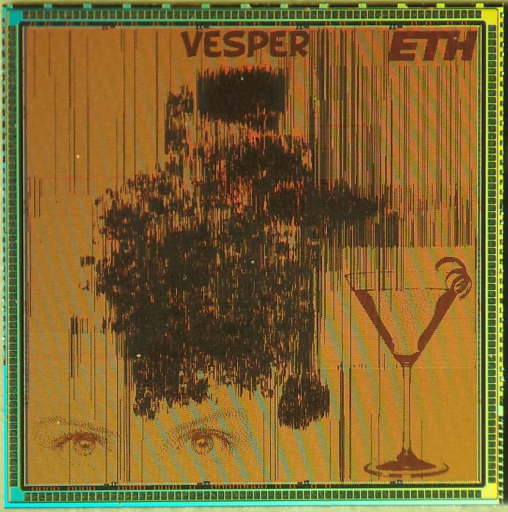

Vesper (2011)

Additional pictures below, click to see larger versions

by

| Application | Graphics |

| Technology | 130 |

| Manufacturer | UMC |

| Type | Master Thesis |

| Package | PGA256 |

| Dimensions | 5000.00μm x 5000.00μm |

| Gates | 1800 kGE |

| Voltage | 1.2 V |

| Clock | 180 MHz |

In this project a non-linear video rendering engine, where each frame is warped into a new frame with an arbitrary per-pixel non-linear warping function is realized. High-quality HD rendering requires large computational resources as well as high memory bandwidth. We target a real-time rendering system that is able to process full HD (1920x1080) video at 30 frames per second (fps). The rendering system comprises of this ASIC, performing the actual rendering operation, and a PCB that contains the ASIC and associated components such as HD video interface and memory blocks.

This design is a continuation of Esper. The main focus of this work was to extend the design to support full HD and to add interfaces to commercially available components such as QDRII SDRAM and DVI. Two clock domains decouple the high-performance rendering part from the fixed rate DVI interface. The inputs of the ASIC are streamed via a high-speed connector from an FPGA base-board.

The name is derived from Vesper Lynd of James Bond franchise. There is a logo of a Vesper cocktail on the chip for this purpose