The IIS Chip Gallery

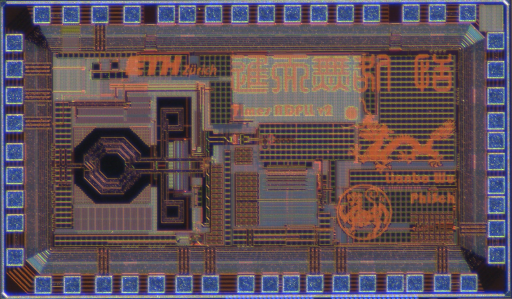

Times_ADPLL_v2b (2019)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | SMIC |

| Type | Research |

| Package | QFN32 |

| Dimensions | 1895μm x 1093μm |

| Voltage | 1.2 V |

| Power | < 5/8 mW (@40/80MHz, 1.2V) |

| Clock | in:40 MHz out:3 GHz |

A 3GHz, sub-200 fs_rms -jitter fractional-N DPLL with a fully differential voltage sampling phase detector is implemented, which resolves the fractional phase error with the help of high performance data converters in voltage domain. Implemented in 130nm CMOS the circuit consumes 5+mW reaching an state-of-the-art FOM. Version a and b denote the differences in the feedback loop implementation.

The logo on the chip is in ancient seal style Chinese font. This word is inspired by the famous book which originates the concept of Yin-yang the book of Changes which was written 3000+ years ago. The word is adapted from the Nine in the 4th place which literally means: