The IIS Chip Gallery

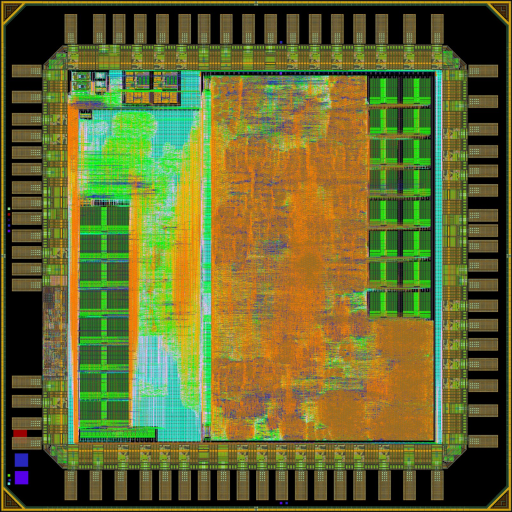

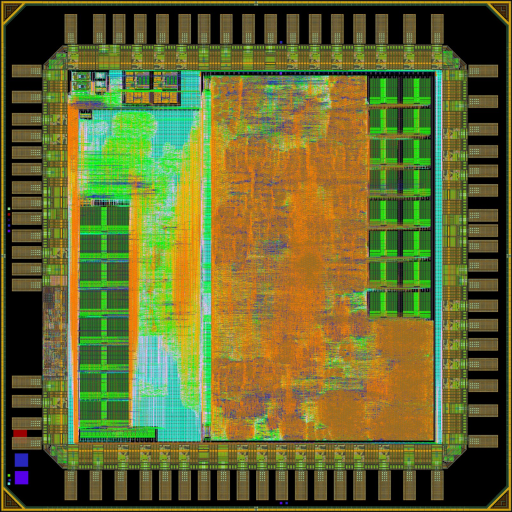

Pulpv3 (2015)

by

| Application | Pulp |

| Technology | 28 |

| Manufacturer | STM |

| Type | Research |

| Package | QFN64 |

| Dimensions | 1650μm x 1650μm |

| Gates | 2500 kGE |

| Voltage | 1.0 V |

| Power | 1.2 mW @ 0.6V, 50MHz |

| Clock | 66 MHz @ 0.6V supply MHz |

Parallel Ultra Low power Processor (PULP) is a shared data memory, parallel processor architecture. This is the third version:

This version of the chip was implemented using ST28 FDSOI technology with RVT transistors. It contains one cluster with 4 OpenRISC cores modified to have much higher IPC and a dedicated DMA controller. In total 128 kBytes of L2, 48 kBytes of TCDM (32 kByte SRAM + 16 kBytes of SCM) are included. There is a shared 4 kBytes 4 way set associative instruction cache for the processor cores using SCMs. The chip includes two body bias regions, and for each region can genarate on chip body bias voltages from -1.8V to Vdd/2 + 0.3V. Other low power features include two on chip FLLs, and the cluster can be completely shutdown. In addition there is also a dedicated hardware accelerator for 2D convolutions integrated.

The chip also features a hardware convolution engine optimized for energy efficiency and bandwidth consumption with a peak performance of 1x 16-bit pixels per cycle.

The chip has been designed in collaboration with University of Bologna, EPFL, CEA-LETI and ST Microelectronics Grenoble